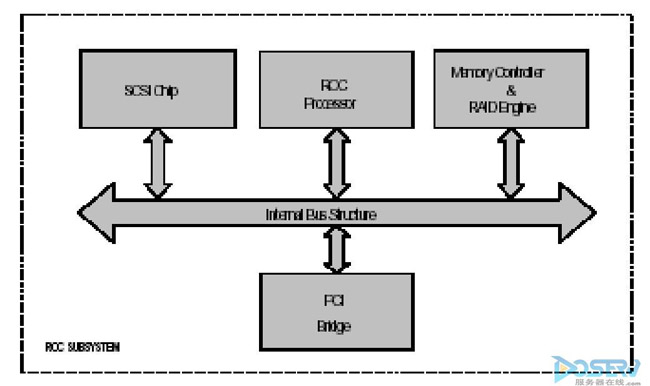

來源:【服務器在線】 通過將一些不相關的組件進行組合并在一個集成電路中相連接,惠普公司開發了全集成硬件RAID解決方案。ROC 子系統包括處理器、內存控制器、硬件RAID引擎、SCSI芯片、PCI橋和一個內部總線結構,所有這些組件組成了一個單獨的底層結構。

惠普公司 ROC 子系統簡易模塊圖

處理器

在ROC子系統中控制RAID實現的ROC處理器采用的是ARM7 32位RISC核心。為產品特制的固件將信息由外部的只讀閃存(ROM)讀入ROC內存,并在ROC內部執行,該操作獨立于主機處理器。在ROC子系統實現RAID功能時,主機處理器可以同時處理其他的事物。

SCSI 芯片

SCSI 芯片由兩個內置Ultra-2 SCSI通道組成。其中一個用于支持服務器內置磁盤驅動器。另一個被用來對SCSI磁帶機的支持。當支持設備為6個內置SCSI設備和一個SCSI磁帶機時,SCSI芯片組達到其設計的******性能。雖然第二條通道可以不連接SCSI磁帶機而是用來連接外置存儲部件,但是增加的負載將降低整體 I/O 性能。如果要在外置存儲部件存在情況下獲得高的I/O 性能,惠普公司建議選用高性能的惠普 Smart Array Controller (惠普智能陣列控制器)來對外置存儲系統進行支持。

PCI 橋

PCI橋提供了ROC子系統內部總線結構與服務器PCI總線之間的接口。主機處理器通過PCI橋與ROC處理器進行通訊。

內部總線結構

ROC內部總線結構由一些在ROC子系統內部組件之間提供通訊通路的內嵌總線構成。這個結構在密集環境中的處理器、內存和存儲器之間提供高可靠性信息和數據控制。內部總線結構通過PCI橋與主機處理器相聯接。

內存控制器和RAID引擎

ROC內存控制器采用內置接口與位于主板上的動態隨機存取存儲器(DRAM),閃存,和非易失性靜態隨機存取存儲器 (SRAM) (圖 10)相連接。RAID引擎控制RAID 5實現中的奇偶校驗。

圖10. ROC內存控制器與主板內存資源接口模塊圖。

SRAM

SRAM的使用取決于ROC程序代碼。SRAM 是非易失性內存,其中存儲著數據重構時子系統的狀態。如果重構過程中電源失效,SRAM中的數據可使子系統由電源失效前的時間點繼續重構進程。

閃存

閃存提供到主機處理器的初始代碼以及到ROC處理器的程序代碼。

DRAM

DRAM 被用于存儲ROC程序代碼和操作數據,同時作為前讀緩存。

該緩存使用智能前讀算法來預估所需數據以減少等待時間。它可以對單個或多個線程中的順序讀取操作進行跟蹤并預先判斷接下來的順序讀取操作。它可以在數據請求真正發生前,從磁盤中前讀或預讀出數據。而當數據請求發生時,從高速緩存中提取數據的速度將是從磁盤中毫秒級提取速度的幾百甚至上千倍。

這種適應性前讀設計對于小塊順序讀取請求有著極佳的性能表現。同時由于在非順序讀取情況下前讀機制被關閉,因此對于隨機讀取模式也沒有不良影響。